# Briki MBC-WB

### Wi-Fi & Bluetooth Device

#### OVERVIEW

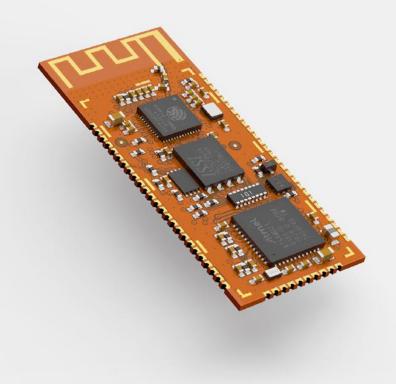

This compact System on module (SoM) is the ideal solution for designers who want a unique device with Wi-Fi & Bluetooth plus a dedicated control MCU.

From prototype to product in a simple and fast way

Exposed debug interfaces for both the chips

Small "1-Brick" form factor with many GPIOs

Compatible pinout between all modules in the family

Liquid logic to surpass the classical rigid master/slave topology

Embedded flash memory for both, code and user storage

Dual-level of embedded security, from cloud to boot

Multi-language support (C/C++ and python)

Dual wireless interface (BLE/BT and Wi-Fi)

meteco™ PRODUCTS BRIKI MBC-WB V.1.0

#### **FEATURES**

## Technical information

ATSAMD21G18A ARM® Cortex®-M0+ running at 48MHz

Product size: 38 x 16 mm

ESP32-D0WD dual-core Tensilica Xtensa LX6 running @240MHz

Internal / External QSPI 16-Mbit, 64-Mbit or 128-Mbit flash

PCB Antenna integrated

CryptoAuth ECC608 chip

Format: 1 brick

This product is sold by request as products for industrial use. The MBC module is available in different versions by hardware configuration and functionalities. Depending on your design, you may prefer one version over the other. Contact us to find the best suited for you!

#### **DEVELOPMENT TOOLS**

# Firmware and software tools

Meteca offers a complete firmware solution for both the MCUs, written in C/C++ and fully compatible with Arduino for a fast and simple prototyping process.

All Briki MBCs are completely programmable using the Arduino IDE or a more professional IDE like Visual Studio Code. The latter, in particular, allows customers to program both the MCUs using different programming languages and/or SDK like Microchip's ASF, Espressif's esp-idf or python.

Both the MCUs have their debugging interface exposed on the module's pinout to ensure full control over the firmware implementation. In conjunction with Visual Studio Code, several debugging devices can be used to extensively debug the code: ATMEL ICE (link) for the ARM Cortex MCU and/or Segger J-Link (link), useful for both the Cortex and the Tensilica ESP32.

The software suite offered includes a set of tools specifically designed to allow firmware update procedure (via USB or OTA for both the MCUs), ESP32's memory mapping along with automatic pin-mapping configuration.

Briki DBC Debugger Board Carrier

Briki ABC Advanced Board Carrier

Briki MBC-WB Development Kit

meteca™ PRODUCTS BRIKI MBC-WB V.1.0

TECH SPECS

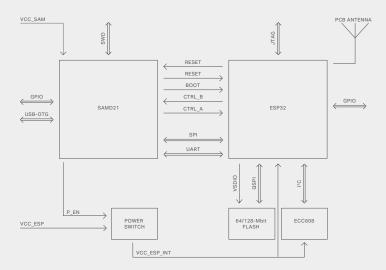

### Block diagram

| ATSAMD21                                                    | ATECC608                                                                                  | ESP32                                                                                                                  |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| PROCESSOR                                                   | CLOUD AUTHENTICATION                                                                      | PROCESSOR                                                                                                              |

| ARM©, Cortex-M0+ CPU up to 48MHz                            | for AWS IoT and Google Cloud IoT Core                                                     | CPU: Xtensa dual-core 32-bit LX6 at 240 MHz and 600 DMIPS                                                              |

| MEMORIES                                                    | HARDWARE SECURITY FEATURES                                                                |                                                                                                                        |

| 256KB in-system self-programmable Flash                     | Cryptographic coprocessor with secure key storage for up to 16 Keys, certificates or data | WIRELESS CONNECTIVITY                                                                                                  |

| 32KB SRAM Memory                                            |                                                                                           | Wi-Fi: 802.11 b/g/n                                                                                                    |

| <u> </u>                                                    | Asymmetric sign, verify, key agreement:                                                   | Bluetooth: v4.2 BR/EDR and BLE                                                                                         |

| SYSTEM                                                      | ECDSA, ECDH, NIST standard P256 elliptic curve support                                    |                                                                                                                        |

| External Interrupt Controller (EIC), 16 exter-              | Support for symmetric algorithms: SHA-256 & HMAC hash including off-chip context          | PERIPHERALS                                                                                                            |

| nal interrupts, one non-maskable interrupt                  |                                                                                           | 10 × GPIOs (touch capacitive sensing)                                                                                  |

|                                                             | save/restore, AES-128 with encrypt/decrypt, galois field multiply for GCM                 | Temperature sensor                                                                                                     |

| LOW POWER                                                   | Networking key management support                                                         | Several digital interfaces like: SPI, I <sup>2</sup> S, I <sup>2</sup> C, UART. SD/SDIO/CE-ATA/MMC/eMMC                |

| Idle and standby sleep modes                                | Turnkey PRF/HKDF calculation for TLS 1.2/1.3                                              | CAN bus 2.0                                                                                                            |

| SleepWalking peripherals                                    |                                                                                           |                                                                                                                        |

| PERIPHERALS                                                 | Ephemeral key generation and key agreement in SRAM                                        | IR controller                                                                                                          |

| 12-channel Direct Mem Access Controller                     |                                                                                           | SECURITY                                                                                                               |

| (DMAC)                                                      | SECURE BOOT SUPPORT                                                                       | IEEE 802.11 featuring WFA,WPA/WPA2, WAPI                                                                               |

| 12-channel Event System                                     | Implementation with ATSAMD21 Cortex-M0+                                                   | Secure boot and Flash encryption                                                                                       |

| Up to five configurable 16-bit Timer/Counters (TC)          | Full ECDSA code signature validation                                                      | 1024-bit OTP, up to 768-bit for customers                                                                              |

|                                                             | Encryption/Authentication for messages to prevent on-board attacks                        | Cryptographic hardware acceleration: AES, SHA-2, RSA, elliptic curve cryptography (ECC), random number generator (RNG) |

| Three 24-bit Timer/Counters for Control (TCC)               |                                                                                           |                                                                                                                        |

| 32-bit Real Time Counter (RTC) with clock/calendar function | ADDITIONAL FEATURES                                                                       | (KNG)                                                                                                                  |

| Watchdog Timer (WDT)                                        | Internal high-quality FIPS 800-90 A/B/C Ran-                                              |                                                                                                                        |

| CRC-32 generator                                            | dom Number Generator (RNG)                                                                |                                                                                                                        |

|                                                             |                                                                                           |                                                                                                                        |

Two high-endurance monotonic counters

Guaranteed unique 72-bit serial number

1MHz Standard I2C interface <150nA Sleep current

sensing I/O

One full-speed USB (12Mbps) Device/Host

Several SERCOM digital interfaces like: I<sup>2</sup>C (up to 3.4MHz), SMBUS/PMBUS, SPI, LIN, UART and analog interfaces like: 12-bit, 350 ksps ADC, 10-bit, 350 ksps DAC, Two Analog Comparators, Peripheral Touch Controller with capacitive touch and proximity capacity IO